# A 7-level Inverter with Multi-Carrier Pulse Width Modulation Technique for PV Systems

# J. N. Bhanutej, Rani Chinnappa Naidu

Abstract: This article presents a Seven –level Inverter with Multi-Carrier Pulse Width Modulation (MCPWM) technique for PV applications.it compares the three major topologies and their Total Harmonics Distortion (THD) for PV applications. Finally, the Cascaded H-bridge inverter is the best and recommend topology for PV applications. These are simulated in MATLAB-Simulink.

Keywords: Multilevel inverter topologies, Multi-Carrier Pulse Width Modulation (MCPWM), Total harmonic distortion.

### I. INTRODUCTION

Rise in Power demand and the lack of enough fossil fuels which doesn't last for long, have pushed man kind in search of renewable energy sources like wind, tidal, and photovoltaic (PV). Among all these, the PV is as an adequate source for clean and green energy generation and gained wide range attention due to advancements in multilevel inverters. The main thing that should be considered in PV system is the grid tied multilevel inverter. Among these solar has been one of the most researched area in recent times due to significant increase in energy conversion and storage technologies. In case of solar Photovoltaic (PV), the energy is harnessed in the form of DC. This DC is converted to AC and fed to utility grid or used for isolated load. Multilevel inverter is a modification of 2-level inverter, which provides 2 output voltages for the load i.e. when a Vdc supply is given as input to the 2-level inverter it will provide +Vdc/2 and -Vdc/2 as output. The harmonic content in the output voltage is high and has a high dv/dt. In multilevel inverters, we deal with more than 2 levels of output voltage hence the name multilevel inverter. The smoothness of the wave is proportional to the number of levels of output voltage[1]. Thereby increasing the voltage levels waveform becomes smoother but this also increases the complexity of the inverter circuit and their Controlling.

There are mainly three different types of multilevel inverters.

- Diode clamped multilevel inverter.

- Flying capacitor multilevel inverter.

- Cascaded H-bridge multilevel inverter.

Revised Manuscript Received on February 28, 2020. \* Correspondence Author

J. N. Bhanutej\*, Assistant .Professor, Department of Electrical and Electronics Engineering, Vignana Bharathi Institute of Technology(VBIT), Rani Chinnappa Naidu, Associate Professor in VIT University, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Advantages of multilevel inverter over two level inverters.

- Reduced harmonic content.

- Output voltage is nearer to sine wave.

- Low dv/dt.

- Switching losses are less.

- Operable at both fundamental frequency and high switching frequency PWM.

#### II. DIODE CLAMPED MULTILEVEL INVERTER

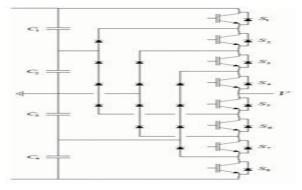

Diode clamped multilevel inverter is first proposed by Nabae, Takashi and Akagi in 1981. It is also called as neutral point converter [2] . It uses clamping diodes in order to limit the voltage stress of power devices. A 3 phase 5 level diode clamped multilevel inverter is shown in the figure 1. All the three phases shares the common dc bus. Which will be divided among the 4 capacitors into five levels. The voltage appearing across each capacitor is Vdc, hence the voltage stress across each switching device is limited to Vdc through the diodes[2].

Fig.1 5 level Diode clamped multilevel inverter

#### III. FLYING CAPACITOR MULTILEVEL NVERTER

This topology developed by Maynard and Foch in 1992. It is similar to that of diode clamped. Unlike diode clamped multilevel inverter it uses a series combination of capacitors instead of diodes to limit the voltage stress of the power devices. These capacitors transfer the limited amount of power to the electronic devices [3]. This topology has a ladder structure of dc side capacitors, where the voltage on each capacitor differs from that of the next capacitor. The voltage increment between two adjacent capacitor legs gives the size of the voltage steps in the output waveform. The main advantage of the Flying capacitor type is that it has redundancies for inner voltage levels. Moreover, the flying capacitor has phase redundancies, whereas the diode clamped has only line – line redundancies.

## A 7-level Inverter with Multi-Carrier Pulse Width Modulation Technique for PV Systems

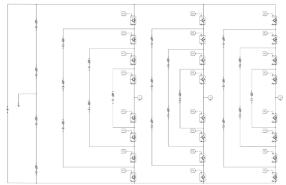

These allow a choice of charging or discharging the capacitors as our need and can be implemented in the control strategies for balancing of the voltages across the different levels. For an N level inverter, we require.2(N-1) switching devices and ((N-1) \*(N-2))/2 auxiliary capacitors per phase[4].

A capacitor clamped inverter is designed and simulated for 3, 5,7 levels and their simulation results are compared. Fig. 2 shows a 5-level flying capacitor inverter simulated in MATLAB/Simulink.

Fig. 2 5-level flying capacitor inverter

### IV. CASCADED H-BRIDGE MULTILEVEL NVERTER

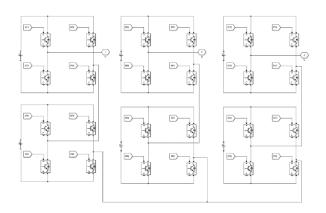

Cascaded H-bridge multilevel inverter is different from the other topologies that we have discussed. Earlier. It requires a smaller number of components. The main drawback of this system is each led i.e. each H-bridge must be connected to a separate dc source. The number DC sources define the number of output voltage levels it is given by m=2s+1. Where n is the number of output levels. Each inverter level can generate three different voltage outputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the dc source to the ac output by different combinations of the four switches,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ . To obtain +V<sub>dc</sub>, switches S<sub>1</sub> and S<sub>4</sub> are turned on, whereas -V<sub>dc</sub> can be obtained by turning on switches S<sub>2</sub> and S<sub>3</sub>. By turning on  $S_1$  and  $S_2$  or  $S_3$  and  $S_4$ , the output voltage is  ${}^30[5]$ . Fig. 3 shows the configuration of a 5 level 3 phase cascaded Hbridge multilevel inverter designed in Simulink and simulated results of it for 3,5,7 levels are presented.

Figure.3 Three-phase 5 level cascaded H-bride inverter

## V. SIMULATION RESULTS

Simulation of the above circuit is carried out in the MATLAB/Simulink. Gating pulses are generated using a

DOI: 10.35940/ijitee.C8543.029420

Journal Website: www.ijitee.org

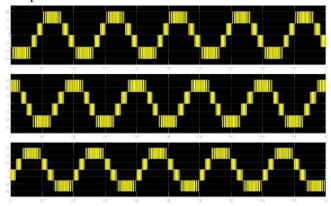

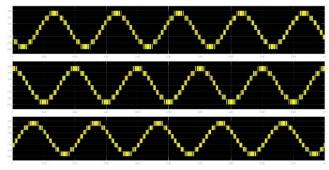

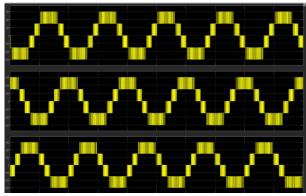

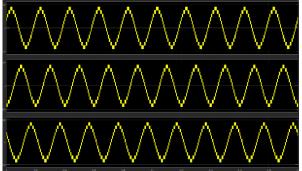

control logic circuit, which uses multicarrier pulse width modulation technique to generate gate pulses in order to control the switching devices. Fig 4, Fig 5 and Fig 6 shows the 3-phase output voltage waveforms of 3,5 and 7 level diode clamped multilevel inverter.

Fig. 4 Three- phase output voltage of 3-level diode clamped multilevel inverter.

Fig. 5 Three- phase output voltage of 5-level diode clamped multilevel inverter.

Fig. 6 Three-phase output voltage of 7-level diode clamped multilevel inverter.

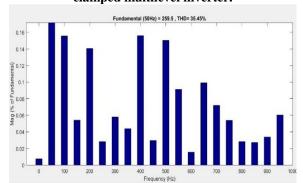

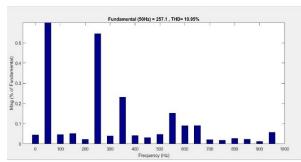

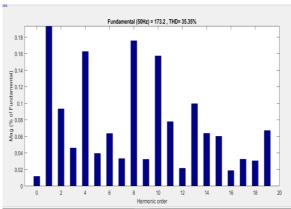

Fig. 7 FFT analysis of a 3-level diode clamped multilevel inverter.

Fig. 8 FFT analysis of a 5-level diode clamped multilevel inverter.

Fig. 9 FFT analysis of a 7-level diode clamped multilevel inverter.

Fig 7,Fig 8, Fig 9 shows the total harmonic content present in the output voltage from the above figures it is evident that as the number of level are increasing the harmonic content in the output waveform is reduced from 35.45 to 10.95 for a 3 level and 7 level inverter respectively.

**Table 1 Total harmonic distortion**

| Number of levels | Voltage THD in % |

|------------------|------------------|

| 3                | 35.45            |

| 5                | 17.34            |

| 7                | 10.96            |

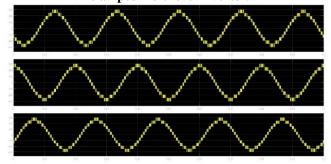

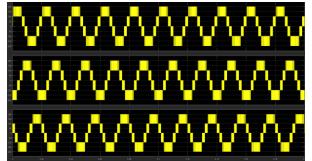

Fig 10, Fig 11 and Fig 12 shows the 3-phase output voltage waveforms of 3,5 and 7 level Flying capacitor multilevel inverter.

Fig. 10 Three- phase output voltage waveforms of 3 level inverter

Fig. 11 Three-phase output voltage waveform of 5 level inverter

Fig. 22 Three-phase output voltage waveform of 7 level inverter

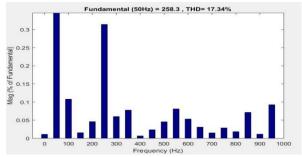

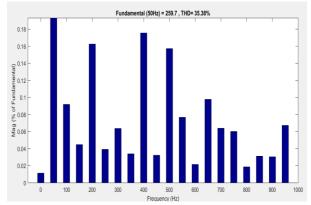

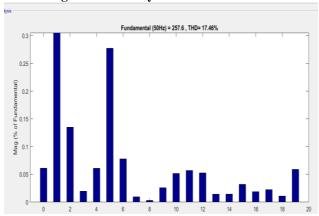

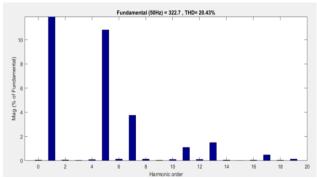

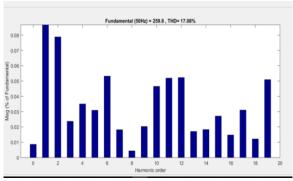

Fig. 13 FFT analysis of 3-level inverter

Fig. 14 FFT analysis of 5-level inverter

Fig. 3 FFT analysis of 7-level inverter

Fig 13, Fig 14 and Fig 15 shows the total harmonic distortion in the output voltage waveform and the Table 2 shows the comparison between the THD for various levels of inverters

**Table 2 Total harmonic distortion**

| Number of levels | Voltage THD in % |

|------------------|------------------|

| 3                | 35.38            |

| 5                | 17.46            |

| 7                | 20.43            |

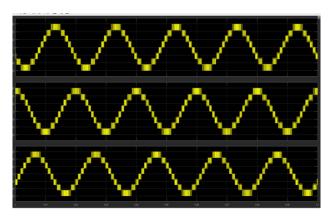

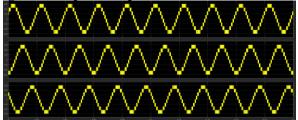

Fig 16, Fig 17 and Fig 18 shows the 3-phase output voltage waveforms of 3,5 and 7 level Cascaded H-Bridge multilevel inverter.

Fig. 4 Three -phase output waveform of 3level inverter

Fig. 5 Three-phase 5 level multilevel inverter

Fig. 6 Three-phase 7level inverter

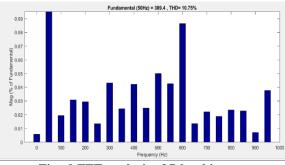

Fig. 7 FFT analysis of 3-level inverter

Fig. 8 FFT analysis of 5-level inverter

Fig. 9 FFT analysis of 7-level inverter

Fig 19, Fig 20. Fig 21 shows 3,5,7 level inverters with their harmonic content in the output voltage waveform expressed in THD % respectively and compared in the Table 3 below.

**Table 3 Total harmonic distortion**

| Number of levels | Voltage THD in % |

|------------------|------------------|

| 3                | 35.35            |

| 5                | 17.08            |

| 7                | 10.74            |

### VI. DATA ANALYSIS

Three types of topologies namely diode clamped, flying capacitor and cascaded H-bridge multilevel inverters are designed, simulated and analyzed for 3,5 and 7 levels of voltage and are compared in terms of THD values. The least THD value obtained by Using Cascaded H-Bridge and it has less number of components compared to others. Table 4 shows the comparison of THD among these three different topologies for 3,5 and 7 level.

**Table 4 Total harmonic distortion**

| Number    | r Voltage THD in % |           |          |  |  |

|-----------|--------------------|-----------|----------|--|--|

| of levels | Diode              | Flying    | Cascaded |  |  |

|           | Clamped            | Capacitor | H-Bridge |  |  |

| 3         | 35.45              | 35.38     | 35.35    |  |  |

| 5         | 17.34              | 17.46     | 17.08    |  |  |

| 7         | 10.96              | 20.43     | 10.74    |  |  |

#### VII. CONCLUSION

This work presents comparative analysis of cascade H-bridge multi-level inverter, Diode-clamped multi-level inverter and flying capacitor multi-level inverter for 3,5 and 7 levels. These are simulated and analysed for Total harmonic distortion using FFT analysis. Looking at the results the Cascaded H-bridge inverter is recommend the best topology for PV applications.

## REFERENCES

- Ahmad, Suziana, et al. "Grid connected multilevel inverters for PV application." 2015 IEEE Conference on Energy Conversion (CENCON). IEEE, 2015.

- Rajesh, B. "Comparison of harmonics and THD suppression with three and 5 level multilevel inverter-cascaded H-bridge." 2016 International Conference on Circuit, Power and Computing Technologies (ICCPCT). IEEE, 2016.

- Khomfoi, Surin, and Leon M. Tolbert. "Multilevel power converters." Power electronics handbook. Butterworth-Heinemann,

- Jiang, Xueyang, and Mamadou Lamine Doumbia. "Comparative Study of Grid-Connected Multilevel Inverters for High Power Phtovoltaic Systems." 2019 IEEE 7th International Conference on Smart Energy  $Grid\ Engineering\ (SEGE).\ IEEE,\ 2019.$

- Munjer, M. A., et al. "Minimization of THD for Multilevel Converters with triangular injection approach." 2018 3rd International Conference for Convergence in Technology (I2CT). IEEE, 2018.. [5] Joca, Davi R., et al. "THD analysis of a modulation technique applied for thd reduction." 2013 Brazilian Power Electronics Conference. IEEE, 2013.

# **AUTHORS PROFILE**

J.N Bhanutej ,Research scholar pursuing his Ph.D in School of electrical engineering (SELECT) VIT-Vellore and working as Assistant .Professor in the department of Electrical and Electronics Engineering at Vignana Bharathi Institute of Technology(VBIT), An Autonomous Institute, Affiliated to Jawaharlal Nehru Technological

University-Hyd. His research area is Multilevel inverters for Renewable energy sources.

Rani. C received the Ph.D. degree in 2014 from the Northumbria University, UK. After that, she joined asa Postdoctoral Researcher in Northumbria Photovoltaic Applications Centre at the Northumbria University, UK. She was graduated with a First-Class BEng andMTech in Electrical Engineering both from the VIT University,

India. At present, she is working as Associate Professor in VIT University, India. She is asenior member of IEEE. She leads an appreciable number of research groups and projects in the areas such as Solar Photovoltaic, wind energy, power generation dispatch, power system optimization and artificial intelligence techniques.