# Advanced Improvement in Speed of Operation of 3-Stage CMOS Ring Oscillator Clock Generation using CPG

G C Arun Kumar, K. Mahalakshmi

Abstract: The Ring oscillator is a member of time delay Oscillators. In this Ring oscillator it uses odd number of inverters and has a gain greater than one. In normal Ring Oscillator architecture the performance is very low due to power gating mechanism. By using CPG technique the performance is increased and also utilizes low power for operation. This Ring oscillator by using CPG technique is affected by pressure and temperature variations. By using 3-stage CMOS ring oscillator the efficiency and performance is increased. In CMOS Ring oscillator power supervision (PS) and efficiency is increased. Most of the architecture is planned for cut back the ability within the IPs to provide power gating, with the task of falling system level control gating. In this CMOS Ring oscillator the output of each NOT gate is given to next stage in order to improve the system latency. For CMOS Ring oscillator, there is no output is given to system, but Reset pulse will drive the entire architecture. In CPG power of the device will change in cyclic manner, device will be ON and OFF over small duration of time. By this proposed method over all power consumption and speed of operation is increased.

Keywords: Power Supervision, IP, Power Gating, CPG.

#### I. INTRODUCTION

In CMOS Ring oscillator, Propagation delay acts important role in integrated circuit design structures that reduces the facility within the IPs like timepiece and control devices. The most important parameters for designing integrated circuit are propagation delay and power consumption and also speed of operation. The Ring oscillator design can be obtained by connecting odd number of inverters in order to obtain better gain of the system. So as to power losing the circuit any, it's to travel to a deeper state, once the system goes through numerous power awake sequences, the get up latency are going to be abundant. To display this example, the generator clock of CMOS is preferred. But the ring generator clock is prone to method, power and Temperature changes; it tends to develop a unique design to cut back PVTA changes. The main objective of this style is to cut back the system speed whereas mortal a lot of proof against PVTA variations.

Revised Manuscript Received on March 30, 2020.

\* Correspondence Author

G C Arun Kumar\*, Department of ECE, Kuppam Engineering College, Kuppam, India. arun27778@gmail.com

Dr. K. Mahalakshmi, Associate Professor, Department of ECE, College, Kuppam Engineering Kuppam, mahakailash123@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

#### II. MOTIVATION

#### A. Problem Statement

There is a desire to produce efficient Ring oscillator Architecture in power gating techniques. A traditional technique involves lot of power consumption and requires more area and logic power.

#### **B. Solution Statement**

This Ring oscillator by using CPG technique is affected by pressure and temperature variations. By using 3-stage CMOS ring oscillator the efficiency and performance is increased. In CMOS Ring oscillator power supervision (PS) and efficiency is increased. Most of the architecture is planned for cut back the ability within the IPs to provide power gating, with the task of falling system level control gating. The major concerning factor is cyclic power gating in Ring Oscillator Architecture.

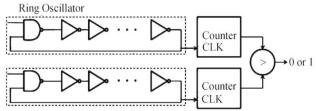

Sometimes the Ring Oscillators do not generate the clock. The frequency is altered by the length of the generator. It contains of associate abnormal inverters connected in the form of chain. A complete  $2\pi$  part shift round the loop at a frequency wherever the small gain is concerning to correct the oscillation [4].

Figure 1: Basic 3-Stage Ring Oscillator Architecture

## C. Objectives

The changes in digital parameters makes area unit variations that origin the circuit to behave in surprising customs in which method variation deviations will occur because of variations within the production process. This will make variations in sheet resistance. All over producing it's impossible to get homogeneous device magnitude for every MOS circuit like semiconductor dimensions can result in variations in threshold voltage and may have an effect on the propagation delay. In an IC different area of chip it exhibits different electrical properties.

#### D. Methodology

The supply voltage provided will depart from the best price. It may arise because of the resistance gift transversely the availability lines. The presence of self inductance of offer lines may also contribute to the voltage fall [11]. Voltage changes will have an effect on the saturation current of the circuit. Since the propagation delay depends on the saturation current, the modification in dip transversely numerous areas of the circuit will affect distinction in propagation delay across completely different areas.

Power dissipation in the circuit leads to change in the temperature of circuit in different areas. This may occur because of change, short and leak power of the circuit. With the rise in temperature at an exact purpose quality of electrons and holes can begin to reduce, because of this, it will cause increase in delay. Elevated temperature may also cause shrink in threshold voltage which might successively result in decrease in delay. But the decrease in quality has the larger result on delay. The Power utilization in SOCs is one of the most important concerns that the today silicon industry is facing recently [10]. To get better power utilization problem, CMOS Ring Oscillator with CPG technique is introduced. Due to better gain of inverters present in the Ring oscillator power of the device is also minimized [5].

In CMOS two types of power dissipation takes place namely static and dynamic power dissipation. Static power dissipation occurs due to when the device is in standby mode. Dynamic power dissipation is essentially when the circuit is in active condition. In dynamic there is clock present in the circuit which leads to power dissipation. Dynamic power is caused to change in switching operation of the device. In CMOS device both pull up and pull down network is present which leads to change the operation of the device. The powers dissipated due to pull up and pull down network due to charging and discharging of capacitor is called switching power dissipation [9]. If it has a tendency to square measure handling a circuit operating underneath an especially high frequency, the facility dissipation is terribly high. But the disadvantage of this power dissipation is that it affects the performance and latency of the system.

The opposite technique is by reducing load capacitance, however this resolution is difficult to implement because it needs careful circuit style exploitation fewer wires. If the circuit isn't change, in theory it's expected that it shouldn't consume power.

This current will occur although the gate voltage is below the edge voltage (off condition). This result is even additional important as it have a propensity to scale down the CMOS circuits since different redundant effects will occur like punch through- wherever through channel length modulation the depletion regions round the supply and drain merge, or tunneling- wherever the gate voltage is high enough specified the charge carrier's tunnel through the chemical compound sheet.

Many techniques are developed for sinking static power dissipation like voltage islands bound giant parts of the circuit is shut faraway from voltage, but this thesis can primarily on handling power wastage during the operation of the device.

#### III. EXISTING SYSTEM

In Structure level there are two types in which of power gating i.e., by splitting up aware power gating and splitting unaware power gating.

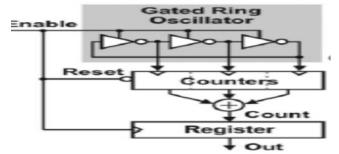

Figure 2: Power Gated Ring Oscillator

It has many drawbacks like giant space is occupied, a lot of power is dissipated, it's stricken by pressure and temperature variations and it uses the PLL clock. Alternative existing style includes label Ring generator Clock by dynamically variable condition consistent with the variable Ring generator (RO) clock frequency even supposing the method corners and conjointly with factors like high temperature and electrical energy as shown in figure.2.

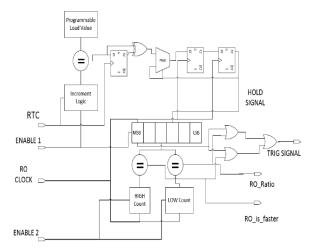

FIgure 3: Structural of calibrated Ring Oscillator

The Ring generator Clock could be a terribly secure tamper proof clock as a result of its internal clock generation. In normal Ring oscillator clock generation the propagation delay is very more and latency will totally depend on number of inverters present in the design structure. This implementation regarding the Ring generator therefore it will be utilized in a proper manner for normal applications in terms of frequency variation. For this to increase the operating speed and latency CMOS Ring oscillator is preferred.

The trigger signal condition is dynamically varied consistent with the variable Ring generator. In existing Silicon on chip display place, reset is supported ring generator clocks attributable to its secure nature. The planned resolution can resolve this issue. With relation to Figure two, there square measure two counters.

One in all those runs on a hoop generator Clock and also the different one runs on a true Time Clock (RTC) equipped outwardly. Victimization the RTC Clock, the Ring generator is tag. This standardization happens solely at the time of boot and it ne'er uses the RTC Clock additional. Upon reset, each Counters start enumeration supported the change condition. Change one are declared once power smart reset is declared and change two are declared once the change one assertion by software package. When RTC Clock Counter reaches the required worth it stops itself and it additionally stops the free running Ring generator Clock Counter. In his way, the Ring generator Clock Counter gets label.

In Ring oscillator due to inverters design the gain of the system will be more and latency and operating speed is increased. It's many drawbacks just like the standardization is performed solely internally, however has the benefits am passionate about it is user label that occupies less space, less power consumption and is quicker in performance.

#### IV. PROPOSED METHOD

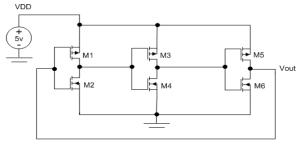

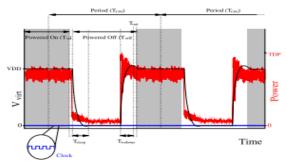

The fundamental unit of Ring Oscillator is an inverter element. This element made up of p-mos and n-mos. This cell is always symmetric in the way of operation. The main part is off and on over little fundamental quantity. Ring oscillator is designed by using odd number of inverters, in which input of inverter is low which makes output to high condition. In this CMOS Ring oscillator design digital parameters are characterized by the operation of device. The power-gating is cyclic, by neutering the quantitative relation of your time spent powered-on and off in every power-gating amount the effective in operation frequency and power consumption of a core may be controlled. The function of Power Gating in Cyclic is shown in Figure.3

This Ring oscillator by using CPG technique is affected by pressure and temperature variations. By using 3-stage CMOS ring oscillator the performance of the device is increased. In CMOS Ring oscillator power supervision (PS) and efficiency is increased. Most of the architecture is planned for cut back the ability within the IPs to provide power gating, with the task of falling system level control gating. The parameters average delay and power consumption will be less compared to existing method.

Figure 5: 3-Stage CMOS Ring Oscillator

By using CMOS ring Oscillator the speed of operation is increased.

Figure 6: Cyclic Power Gating

This design has several advantages like improved performance, less power dissipation and good scaling of power utilization. In this by using CMOS Ring oscillator the operating speed is increased.

#### V. SIMULATION RESULTS

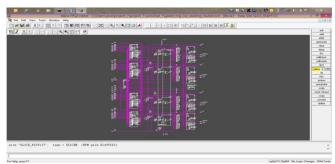

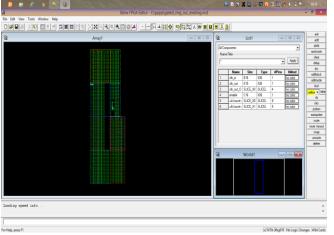

The styles are modeled in Verilog lipoprotein and are functionally verified by victimization Xilinx ISIM Simulation Tool. The styles are synthesized for Spartan3E FPGA by suing Xilinx ISE 14.5 Tools for the device XC3S500E with a package of FG320 and a speed grade of -5.

The simulation wave for power aware ring generator style is shown in figure 4. Wherever the punch out shows the output clock signal from the ring generator. This style is born-again to register transfer logic by the Xilinx synthesizer as shown in figure 5 and to 90nm CMOS technology primarily based LUT mapped schematic as shown in figure 6. The facility aware ring generator style is extracted for FPGA together with its sample routing while not imposing constraints is shown in figure 7.

Figure 7: Elaborated design of Ring oscillator using FPGA

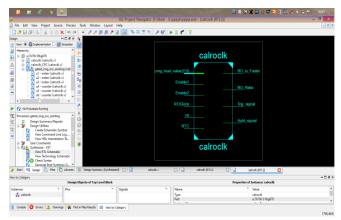

Figure 8: RTL Schematic of ring oscillator using CPG

Figure 9: RTL Schematic of power aware CMOS ring oscillator design

Figure 10: Xilinx FPGA Implementation of CMOS ring oscillator design

The simulation wave form for tag ring generator style is shown in figure 8. This style is reborn to register transfer logic by the Xilinx synthesizer as shown in figure 9 and to 90nm CMOS technology based mostly LUT mapped schematic as shown in figure 10. The tag ring generator style is extracted for FPGA beside its sample routing while not imposing constraints is shown in figure 11.

Figure 11: Design of CMOS gated Ring Oscillator

Figure 12: RTL Schematic of Calibrated CMOS Ring Oscillator Design

Figure 13: Technology Schematic of Calibrated Ring **Oscillator Design**

Figure 14: FPGA Implementation of Calibrated Ring **Oscillator Design**

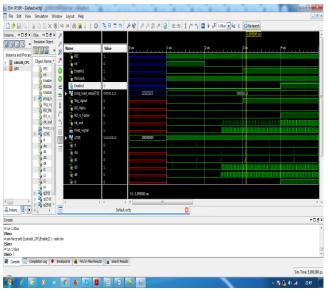

The simulation wave form for cyclic power gated ring generator style is shown in figure 12. This style is reborn to register transfer logic by the Xilinx synthesizer as shown in figure 13 and to 90nm CMOS technology primarily based LUT mapped schematic as shown in figure 14. The cyclic power gated ring generator style is extracted for FPGA alongside its sample routing while not imposing constraints is shown in figure 15.

Figure 15: Simulation Waveforms of cyclic power gated ring oscillator design

Figure 16: RTL Schematic of cyclic power gated ring oscillator design

Figure 17: Technology Schematic of cyclic power gated ring oscillator design

Figure 18: FPGA Implementation of cyclic power gated ring oscillator design

Table-I: Comparison of various Ring Oscillator Designs

| PARAMETERS                 | EXISTING | EXISTING | PROPOSED |

|----------------------------|----------|----------|----------|

|                            | METHOD-1 | METHOD-2 | METHOD   |

| No. of slices              | 18       | 18       | 12       |

| No. of slices of flip-flop | 27       | 27       | 20       |

| Number of 4 input LUT's    | 35       | 34       | 20       |

| Number of<br>bonded IOB's  | 16       | 15       | 10       |

| Number of gated clocks     | 2        | 2        | 2        |

| XPower<br>Analysis(W)      | 0.085    | 0.084    | 0.082    |

| Logic power                | 0.0007   | 0.0003   | 0.0001   |

| Signal Data<br>power(W)    | 0.003    | 0.002    | 0.002    |

| Input/output power(W)      | 0.00420  | 0.00319  | 0.0010   |

| Control power(W)           | 0.0004   | 0.0004   | 0.0002   |

From Table I, it's clear that the planned style slightly will increase the world with a suitable delay however with a discount of 83.7% in logic power and 30.3% in information power. Additionally there's slight increase in fan-out of the planned style.

## VI. CONCLUSION

In IC design architectures, Power management architectures were planned to scale back the ability within the IPs. Swap clock sources were introduced like a hoop generator clock that is at risk of method, Voltage and Temperature variations i.e., a innovative thanks to scale back the system speed by a replacement power design flow with a tag ring generator clock that runs all power Supervision operations on the freshly generated clock is introduced.

# Advanced Improvement in Speed of Operation of 3-Stage CMOS Ring Oscillator Clock Generation using

The most objective of this style is to scale back the system latency and to improve the additional immune digital parameter variations.

During this thesis, a replacement design for CMOS ring generator standardization circuit that is quicker in operating speed and has less space and power compared to the present power supervision design. The planned style slightly will increase the world with a suitable delay however with a discount of 55.7% in logic power and 33.3% in information power. Additionally there's slight increase in fan-out of the planned style.

REFERENCESS

- 1. T. Kidd,"Power Management States: P-States, C-States, and Package  $CS tates, "07-Jun-2017. [Online]. Available: \underline{https://software.intel.com/en} \\$ us/articles/power-management-states-p-states-c-states-and-package-cst ates. [Accessed: 16-May-2018].

- Vanshikha Singh and Rajesh Mehra, "Design and Performance Analysis of Area Efficient CMOS Decoder Circuit," International Journal of Scientific Research Engineering and Technology, pp. 43-48, March

- Dileep J. Kurian, A.K Sreenath, Midhun Krishna. "A Novel Power Management Save-Restore Flow Architecture using Calibrated Ring Oscillator Clock Generation", 2018 IEEE International Conference on System, Computation, Automation and Networking (ICSCA), 2018

- K. Sundaresan, P. Allen, and F. Ayazi, "Process and Temperature Compensation in a 7-MHz CMOS Clock Oscillator," IEEE Journal of Solid-State Circuits, vol. 41, no. 2, pp. 433-442, Feb. 2006.

- K. Sundaresan, K. Brouse, K. U-Yen, F. Ayazi, and P. Allen," A 7-MHz process, temperature and supply compensated clock oscillator in 0.25 m CMOS," Proceedings of the 2003 International Symposium on Circuits and Systems, 2003. ISCAS 03, pp. I-693-I-696, May 2003.

- G. K. Konstadinidis, "Challenges in microprocessor physical and power management design," 2009 International Symposium on VLSI Design, Automation and Test, pp. 9-12, Apr. 2009.

- Cakmakci, Yaman, William Toms, Javier Navaridas, and Mikel Lujan. "Cyclic Power-Gating as an Alternative to Voltage and Frequency Scaling", IEEE Computer Architecture Letters, 2015.

- Anand S. S.B. and Razavi B., "A CMOS clock recovery circuit for 2.5-Gb/s NRZ data," IEEE J.

- M. Li, P. Huang, L. Shen, Z. Zhou, J.-F. Kang and X.-Y. Liu, "Simulation of the RRAM-based flip-flops with data retention," 2016 IEEE International Nano electronics Conference (INEC), pp. 1-2, May 2016

- 10. H.-W. Hsu, S.-H. Kuo, W.-H. Chang, S.-H. Chen, M.-T. Chang and M. C.-T. Chao, "Testing retention flip-flops in power-gated designs," 2013 IEEE 31st VLSI Test Symposium (VTS), pp. 1-6, Apr. 2013.

- 11. Sun L. and Kwasniewski T. A. (2001): 'A 1.25GHz 0.35Pm monolithic CMOS PLL based on a multiphase ring oscillator', IEEE J. of Solid State Circuits, 36, PP. 910-916.

- 12. B. L. Barranco, A. R. Vazquez, E. S. Sinencio, and J. L. Huertas, "Frequency tuning loop for VCOs," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), Jun. 1991, pp. 2617-2620.

- 13. AnandS. B. and RazaviB. (2001): 'A CMOS clock recovery circuit for 2.5-Gb/s NRZ data', IEEE J. Solid-State Circuits, 36, PP. 432–439.

- 14. Sun L. and Kwasniewski T. A. (2001): 'A 1.25GHz 0.35Pm monolithic CMOS PLL based on a multiphase ring oscillator', IEEE J. of Solid State Circuits, 36, PP. 910-916.

- 15. MairH. and XiuL. (2000): 'An architecture of high performance frequency and phase synthesis', IEEE J. of Solid State Circuits, 35, PP. 835-846, 317

- 16. SarkarB. C. and MandalM. K. (2003): 'Ring oscillator based direct digital frequency synthesizer with improved spectral purity', IJEMS, 10, PP. 189- 192

- 17. MandalM. K. and SarkarB. C. (2003): 'new charges pump PLL for tracking bursty signals', IJPAP, 41, PP. 402-407.

# **AUTHORS PROFILE**

Retrieval Number: B7803129219/2020©BEIESP

DOI: 10.35940/ijitee.B7803.039520

Journal Website: www.ijitee.org

G C Arun Kumar, awarded B.Tech (ECE) from Mother Theresa Institute of Engineering and Technology now pursuing M.Tech in the stream of VLSI Design. He is keen interested on exploring various technologies like VLSI Design and Verilog HDL. He is Attended various Conferences,

international seminars and College organized Industrial Visits. His areas of interest are Digital Electronics, Digital communication, Microelectronic Systems and VLSI Design.

Dr. K. Mahalakshmi, is working as Associate Professor in the Department of Electronics & Communication Engineering, Kuppam Engineering College, and Andhra Pradesh, India. She has completed her Doctoral degree from Anna University, Chennai, and Tamilnadu, India. She has published many papers in international journals

and conferences and registered patent in Hydroponics Agriculture. She has been appointed by Anna University Chennai as Indian examiner to review Ph. D thesis. Her areas of interest are Ad hoc Networks, IoT and Embedded